输入或输出端并联的电容如果掉了,起码电源还能输出一个目标电压(稳定性和噪声性能差),但是如果CBOOT电容异常,电源就完全不会工作。

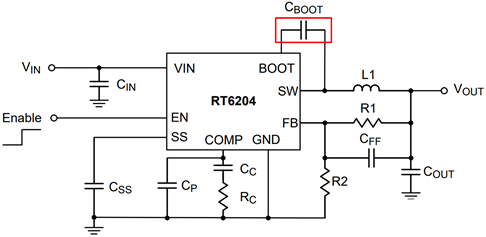

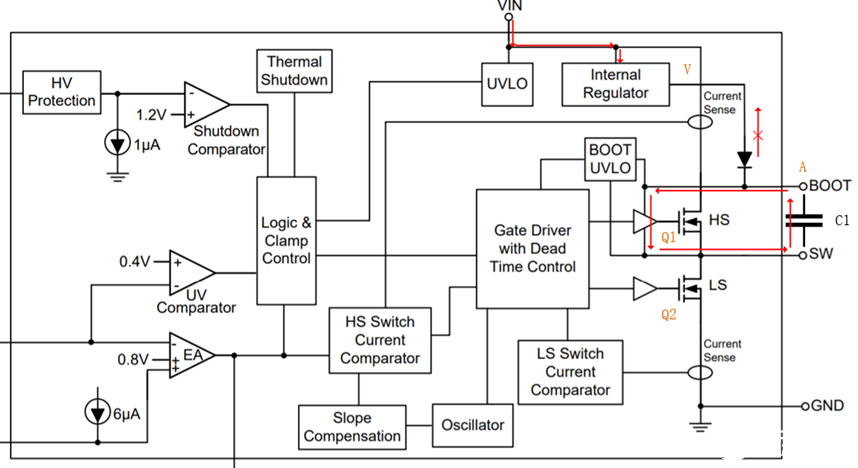

为什么要用自举电路呢?这是因为在一些电路中使用MOS搭建桥式电路,见图1-45 ,下管NMOS导通条件容易实现,下管Q2的栅极G与源极S之间的电压VGS超过VGS(th)后即可导通,VGS(th)通常比较低,因此很容易实现。而对于上管Q1而言,源极S本来就有一定的电压,如果要想直接驱动栅极G来满足VGS>

VGS(th)的条件,栅极G的电压需要比源极S的电压还要高,则需要在栅极G和地之间加一个很高的电压,这个难以实现(MOS相关介绍见1.5小节)。

有了自举电路,就可以轻松在上管栅极G产生一个高压,从而驱动上管MOS。具体原理如下:

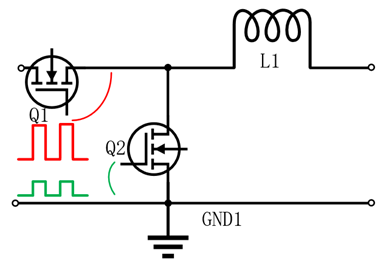

见书图1-46 ,输入总电压VIN经过internal regulator后输出一个直流电压V,用于给CBOOT(C1)充电,这个internal regulator一般是LDO结构的电源(LDO原理在第二章有详细介绍)。当下管Q2导通时,SW电压为0,LDO输出电压V—>

二极管自举电容C1—>

下管Q2—>

地,通过这条回路对CBOOT电容进行充电,电容两端两端电压约等于V。

当下管Q2断开时,电容放电路径见图1-47 ,SW位置电压不再是0,不管SW位置的电压是多少,电容C1两端已经存储了电压V,那么A点电压现在比SW位置电压高了V,相当于Q1的栅极G比源极S高了电压V,可以使得上管Q1导通,此时A点的电压变为V+Vsw,实现了电压抬升,电容自己把自己的电压举了起来。

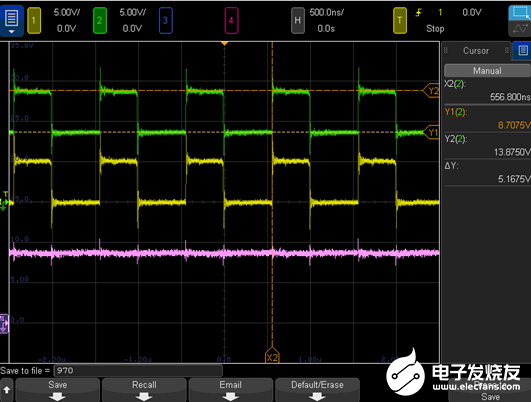

图1-48 是自举电容电压实测波形,黄色和绿色曲线分别是电容两端相对于系统GND的电压波形,粉色是绿线减黄线,是电容两端的电压波形。可以看到随着管子的开关,电容两端的电压一直不变,保持为内部LDO的电压,而电容两端相对于系统GND的电压一直在波动,一会被升上去,一会又降下来,这样就可以在需要的时候,使得电容高边的电压足够高,以驱动上管导通,与前文分析的过程一致。

对Buck电路输出特性的影响 /

电路,通过单片机控制S_OUT为高低电平控制MOS管AOD424的开启关断,利用

电压不能瞬变的特性,使Q10开启时,S_Boost_Out电压高于IN_VOLT

?DCDC BUCK芯片有一个管脚叫BOOT,有的叫BST,如下是一个DCDC芯片对BOOT管脚的解释,在外部电路设计时,BOOT和SW管脚之间,需要加一个

【嘉德点评】思瑞浦的此项发明,通过将BOOT参考电压单元的下端连接到第二输出端SW,解决了轻载情况下

无法充电问题。思瑞浦的产品不仅满足了通信系统中部分关键芯片的严格要求,而且还应

) 的配置。如果它连接到 GND 并且 Vs 迅速下降,例如当负载调节不佳的电源看到电流发生阶跃变化时,

通过二极管接到VCC端,下接上MOS管的S极。当驱动电路驱动下MOS管导通时,VCC通过二极管、RBOOT、下MOS管,对

的作用是什么 /

电路仅仅需要一个15~18V的电源来给逆变器的驱动级提供能量,所有半桥底部IGBT都与这个电源直接相连,半桥上部IGBT的驱动器通过电阻Rboot和二极管VF连接到电源Vb上,每个驱动器都有一个

的选取 /

(bootstrap capacitor)是一种重要的电路元件,它主要用于增加电源或信号电平。它在电源单元、放大器设计、DC/DC转换、PWM控制等电路中广

器,能够在没有外电源的情况下对电场进行储存和放电。其产生原理主要基于自电势和欧姆定律的基本原理

【MAX17502实测】一颗小芯片 满足低压到高压全场景的高效能电源体验

AMD Versal AI Edge自适应计算加速平台PL LED实验(3)

嵌入式学习-飞凌ElfBoard ELF 1板卡-控制wifi模块8723du断/上电