CMOS逆变器短路功耗的仿真

栏目:行业资讯 发布时间:2024-05-30

在逻辑电平转换期间,电流短暂地流过两个晶体管。本文探讨了由此产生的功耗,并为测量电流和功率提供了一些有用的 在本系列的第一篇文章中,我们研究了CMOS反相器的动态和静态功耗。在随后的文章中,我们使用LTspice模拟来进一步了解电容充电和放电引起的功耗。作为讨论的一部分,我们创建了如图1所示的LTspice反相器电路。 我们将在本文中继续使用上述原理图,研究“短路”或“击穿”电流。这两个术

在逻辑电平转换期间,电流短暂地流过两个晶体管。本文探讨了由此产生的功耗,并为测量电流和功率提供了一些有用的

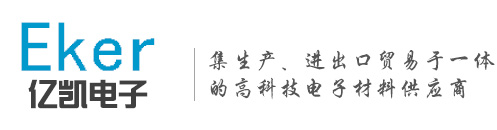

在本系列的第一篇文章中,我们研究了CMOS反相器的动态和静态功耗。在随后的文章中,我们使用LTspice模拟来进一步了解电容充电和放电引起的功耗。作为讨论的一部分,我们创建了如图1所示的LTspice反相器电路。

我们将在本文中继续使用上述原理图,研究“短路”或“击穿”电流。这两个术语指的是在输出过渡期内流经图1中NMOS和PMOS晶体管的电流。

短路电流是可能的,因为随着输入电压——控制两个晶体管的栅极电压——的变化,反相器通过一个电区域,在该电区域中NMOS沟道和PMOS沟道都是导电的。

我们只想测量由于击穿而从VDD流到地的电流。这意味着我们必须排除在转换期间对负载电容器C1充电和放电的电流。

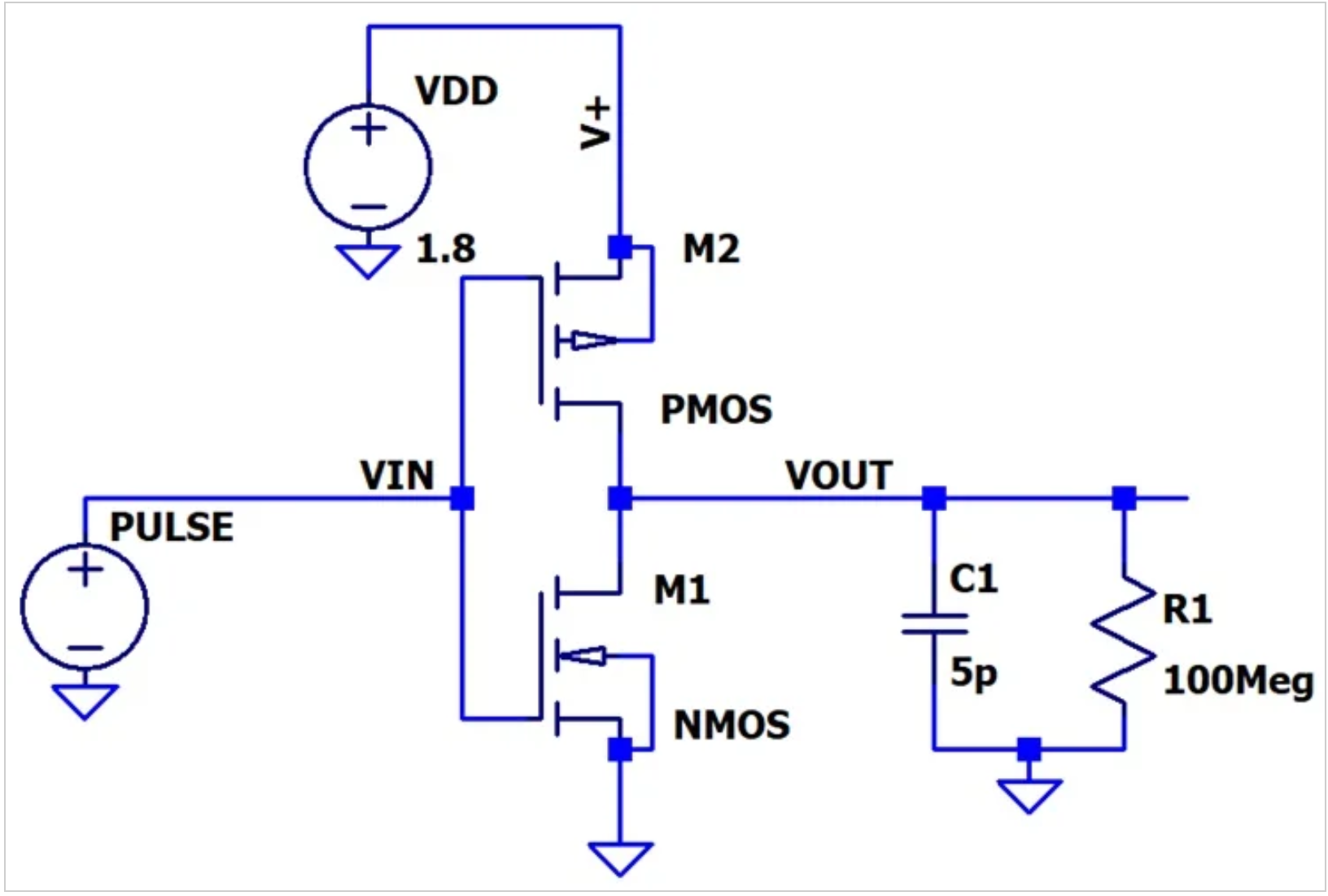

在图2中,我们放大了逆变器电路的中心部分。低至高输出转变的探针位置由NMOS晶体管(M1)的漏极处的绿点示出。

通过探测图2中绿点标记的线段,我们测量了充电电流转向电容器后流过两个晶体管的电流。仿线所示。

仿真旨在为分析CMOS逆变器中的动态功耗提供一个工具包。本着这种精神,在我们结束之前,我想再介绍一个LTspice功能。虽然它不会帮助我们找到任何关于短路功率的其他信息,但它与更广泛的动态功耗主题完全相关。