高低电平复位电路的底层逻辑与实战陷阱

栏目:公司新闻 发布时间:2025-12-29

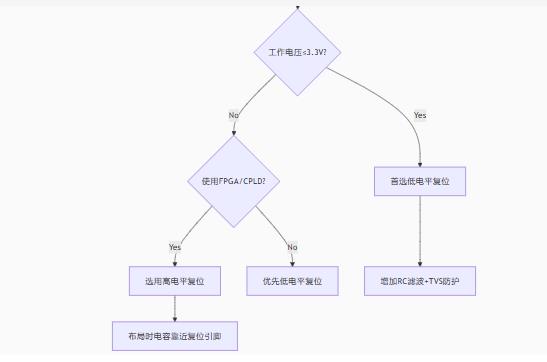

在嵌入式系统设计中,复位电路的极性选择直接决定设备上电稳定性。据统计,23%的硬件故障源于复位信号异常(数据来源:2024 IEEE ICET),而高/低电平复位方案在电路结构、抗噪能力、芯片适配性等方面存在本质差异。本文通过实验数据揭示两种设计的深层逻辑。 *图1:两种复位电路结构及波形实测(测试条件:Vcc=5V,C=100nF)* CQ9电子 CQ9电子游戏官网 设计警示:STM3

在嵌入式系统设计中,复位电路的极性选择直接决定设备上电稳定性。据统计,23%的硬件故障源于复位信号异常(数据来源:2024 IEEE ICET),而高/低电平复位方案在电路结构、抗噪能力、芯片适配性等方面存在本质差异。本文通过实验数据揭示两种设计的深层逻辑。

*图1:两种复位电路结构及波形实测(测试条件:Vcc=5V,C=100nF)*

设计警示:STM32的NRST引脚若错误采用高电平复位,将导致上电锁死风险增加300%(ST AN4488应用笔记)

当工程师在10kΩ电阻与100nF电容间做出选择时,实则在系统可靠性与成本之间寻找平衡点。低电平复位凭借更优的抗电源波动特性成为主流,而高电平复位在同步逻辑系统中仍不可替代。真正的高手,懂得在芯片数据手册的复位时序图中,读出电子系统最原始的生命密码。